## 特点

- 8 路同步采样输入

- 双极性模拟输入范围:  $\pm 10V$ 、 $\pm 5V$

- 完全集成的数据采集解决方案

- $1 M\Omega$  输入阻抗的二阶抗混叠滤波器

- 数字滤波器提供过采样功能

- $88dB$  SNR,  $-102dB$  THD

- $\pm 1.5LSB$  INL,  $\pm 0.8LSB$  DNL

- 灵活的并行/串行接口

- 低功耗:  $100mW$  (典型)

- 待机功耗:  $25mW$  (典型)

## 推荐工作条件

- 电源电压 ( $AV_{CC}$  到  $AGND$ ):

$4.75V \sim 5.25V$

- 电源电压 ( $V_{DRIVE}$  到  $AGND$ ):

$2.3V \sim 5.25V$

- 工作环境温度 ( $T_A$ ):  $-55^{\circ}C \sim 125^{\circ}C$

## 绝对最大额定值

- 电源电压 ( $AV_{CC}$  到  $AGND$ ):

$-0.3V \sim +7V$

- 电源电压 ( $V_{DRIVE}$  到  $AGND$ ):

$-0.3V \sim AV_{CC}+0.3V$

- 模拟输入到  $AGND$ :  $\pm 16.5V$

- 数字输入到  $DGND$ :

$-0.3V \sim V_{DRIVE}+0.3V$

- 数字输出到  $DGND$ :

$-0.3V \sim V_{DRIVE}+0.3V$

- $REFIN$  到  $AGND$ :  $-0.3V \sim AV_{CC}+0.3V$

- 贮存温度 ( $T_{STG}$ ):  $-65^{\circ}C \sim 150^{\circ}C$

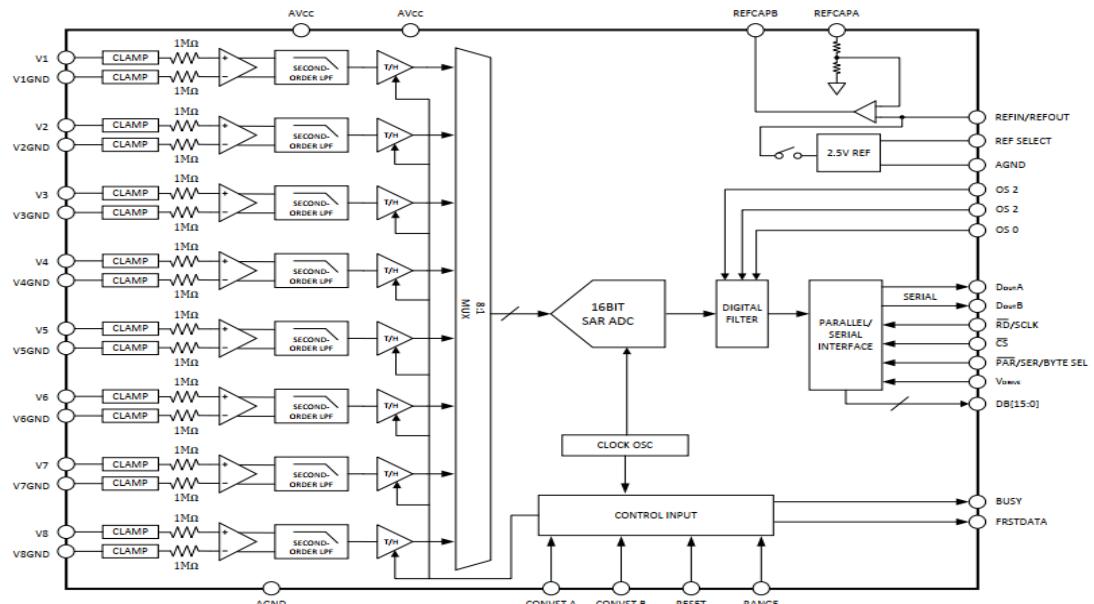

## 简介

XHT7606是一款内置八通道同步采样模数数据采集系统(DAS)。包含了二阶抗混叠滤波器、跟踪保持放大器、16位电荷再分配逐次逼近型模数转换器(ADC)、灵活的数字滤波器、 $2.5V$  基准电压源、基准电压缓冲以及高速串行和并行接口。

XHT7606采用  $5V$  单电源供电，可以处理  $\pm 10V$  和  $\pm 5V$  双极性输入信号，同时所有通道均能以高达  $200kSPS$  的吞吐速率采样。XHT7606的模拟输入阻抗均为  $1M\Omega$ 。它采用单电源工作方式，具有片内滤波和高输入阻抗，因此无需驱动运算放大器和外部双极性电源。内部的抗混叠滤波器的  $3dB$  截止频率为  $22kHz$ ；当采样速率为  $200kSPS$  时，它具有  $40dB$  抗混叠抑制特性。数字滤波器采用引脚驱动，可以改善信噪比(SNR)，并降低  $3dB$  带宽。

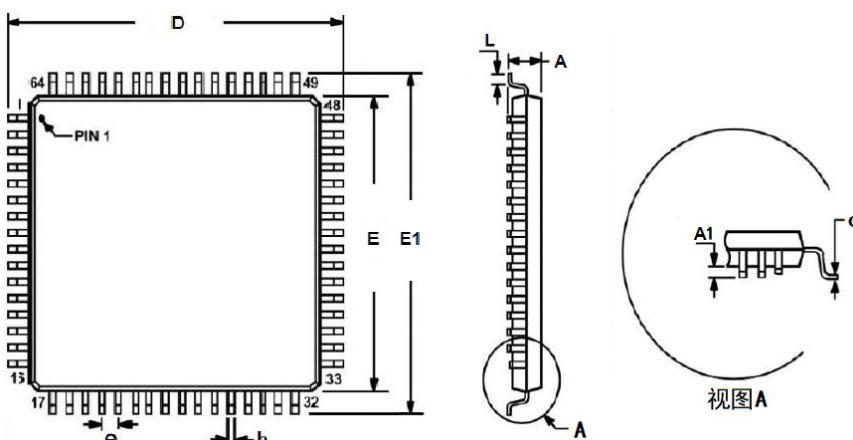

封装形式: 塑封 LQFP64

质量等级: GJB7400 N1 级

## 电特性

| 符号         | 特性        | 条件(除另有规定外,<br>$AV_{CC}=5V$ , $V_{DRIVE}=3V$ ,<br>$f_{sample}=200kSPS$ ,<br>$-55^{\circ}C \leq T_A \leq 125^{\circ}C$ ) | 极限值             |                | 单位  |

|------------|-----------|------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|-----|

|            |           |                                                                                                                        | 最小              | 最大             |     |

| $V_{REF}$  | 基准电压      | —                                                                                                                      | 2.475           | 2.525          | V   |

| $V_{IH}$   | 数字输入高电平电压 | —                                                                                                                      | $0.9V_{DRIVE}$  | —              | V   |

| $V_{IL}$   | 数字输入低电平电压 | —                                                                                                                      | —               | $0.1V_{DRIVE}$ | V   |

| $V_{OH}$   | 数字输出高电平电压 | $I_{OUT}=-100\mu A$                                                                                                    | $V_{DRIVE}-0.2$ | —              | V   |

| $V_{OL}$   | 数字输出低电平电压 | $I_{OUT}=100\mu A$                                                                                                     | —               | 0.2            | V   |

| $V_{IN}$   | 模拟输入电压范围  | RANGE=1                                                                                                                | -10             | 10             | V   |

|            |           | RANGE=0                                                                                                                | -5              | 5              | V   |

| $I_{TOTQ}$ | 工作电源电流    | $f_{sample}=200kSPS$                                                                                                   | —               | 32             | mA  |

| $I_{SB}$   | 休眠电源电流    | —                                                                                                                      | —               | 11             | mA  |

| $I_{SD}$   | 关断电源电流    | —                                                                                                                      | —               | 10             | uA  |

| $SNR$      | 信噪比       | 16 倍过采样, $f=130Hz$ , $\pm 5V$                                                                                          | 83.5            | —              | dB  |

| $SINAD$    | 信纳比       | 无过采样, $\pm 5V$                                                                                                         | 83              | —              | dB  |

| $THD$      | 总谐波失真     | —                                                                                                                      | —               | -90            | dB  |

| $E_{IN}$   | 积分线性误差    | —                                                                                                                      | -5              | 5              | LSB |

| $E_{DL}$   | 微分线性误差    | —                                                                                                                      | -3              | 3              | LSB |

| $RES$      | 分辨率       | —                                                                                                                      | 16              | —              | bit |

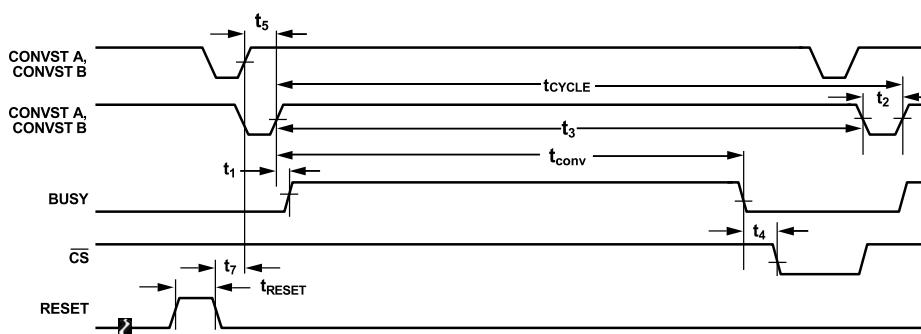

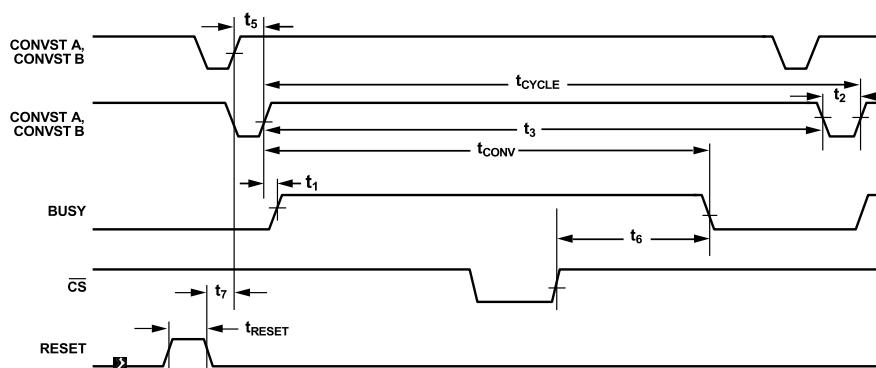

## 时间参数

|                |                            |                                  |      |      |    |

|----------------|----------------------------|----------------------------------|------|------|----|

| $t_{CONV}$     | 转换时间                       | 过采样关闭                            | 3.50 | 4.80 | us |

|                |                            | 64倍过采样                           | 260  | 350  | us |

| $t_{WAKE}$     | 待机模式上电时间                   | $\overline{STBY}$ 上升沿到CONVSTx上升沿 | —    | 120  | us |

| $t_{SHUT}$     | 内基准关断模式上电时间                | $\overline{STBY}$ 上升沿到CONVSTx上升沿 | —    | 35   | ms |

| $t_{RESET}$    | RESET高电平脉冲                 | —                                | 50   | —    | ns |

| $t_{OS\_SET}$  | BUSY到OSn设置时间               | —                                | 20   | —    | ns |

| $t_{OS\_HOLD}$ | BUSY到OSn保持时间               | —                                | 300  | —    | ns |

| $t_1$          | CONVSTx高电平到BUSY高电平         | —                                | —    | 100  | ns |

| $t_2$          | 最小CONVSTx低电平               | —                                | 100  | —    | ns |

| $t_5$          | CONVSTA/CONVSTB上升沿最大容许延迟时间 | —                                | —    | 0.5  | ms |

| $t_7$          | RESET低电平到CONVSTx高电平的延迟时间   | —                                | 50   | —    | ns |

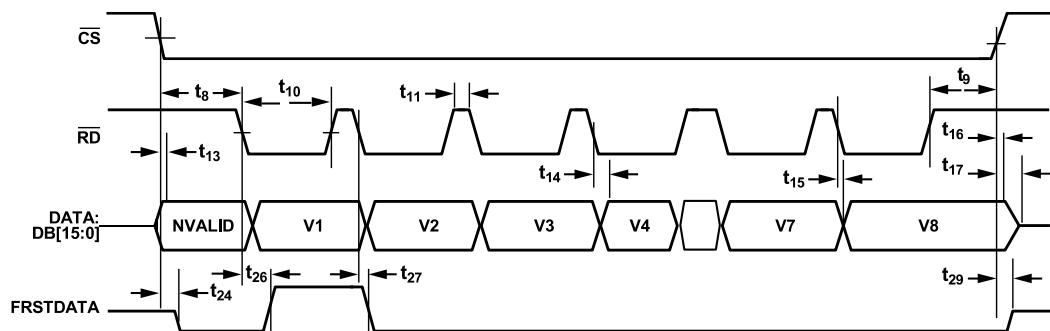

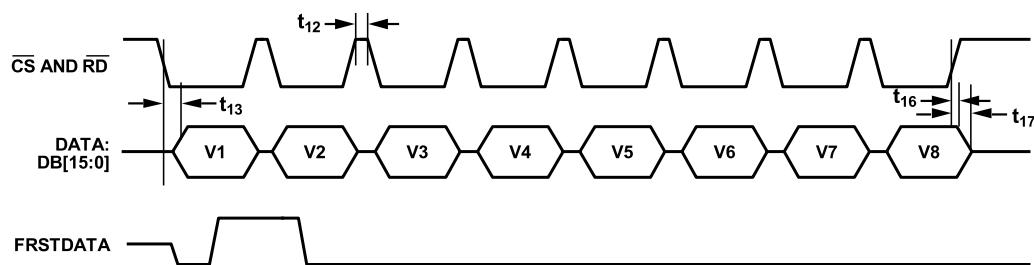

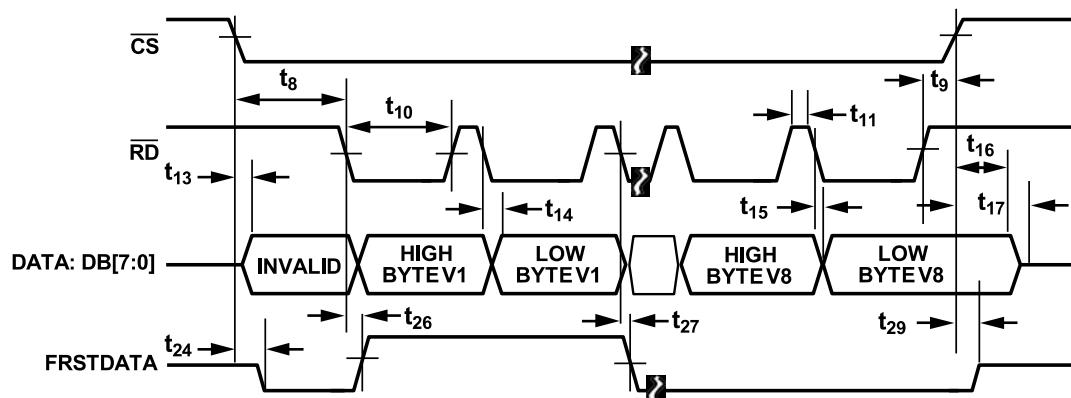

## 并行/字节读取操作

|          |                                    |   |    |    |    |

|----------|------------------------------------|---|----|----|----|

| $t_{10}$ | $\overline{RD}$ 脉冲宽度               | — | 25 | —  | ns |

| $t_{12}$ | $\overline{CS}$ 高电平宽度              | — | 22 | —  | ns |

| $t_{13}$ | $\overline{CS}$ 到D8[15:0]三态禁用的延迟时间 | — | —  | 25 | ns |

| 符号                 | 特性                                    | 条件(除另有规定外,<br>$AV_{CC}=5V$ , $V_{DRIVE}=3V$ ,<br>$f_{sample}=200kSPS$ ,<br>$-55^{\circ}C \leq T_A \leq 125^{\circ}C$ ) | 极限值 |    | 单位  |

|--------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|----|-----|

|                    |                                       |                                                                                                                        | 最小  | 最大 |     |

| $t_{14}$           | RD下降沿的数据访问时间                          | —                                                                                                                      | —   | 25 | ns  |

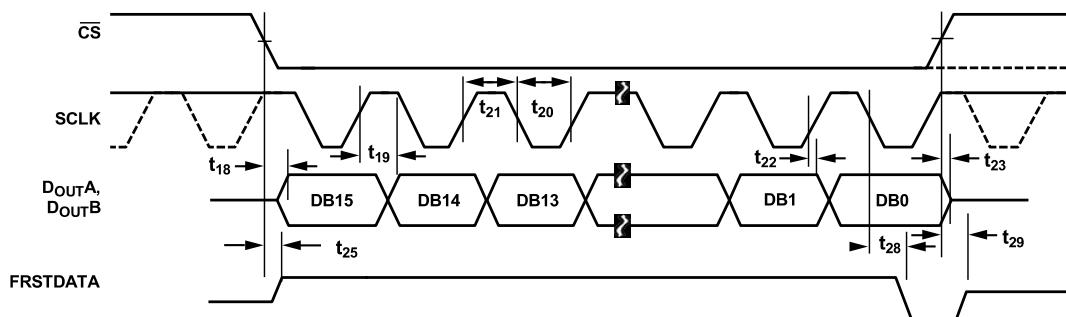

| <b>串行读取操作</b>      |                                       |                                                                                                                        |     |    |     |

| $f_{SCLK}$         | 串行读取时钟                                | —                                                                                                                      | —   | 15 | MHz |

| $t_{18}$           | $\overline{CS}$ 到DOUTx三态禁用的延迟时间       | —                                                                                                                      | —   | 25 | ns  |

| $t_{19}$           | SCLK上升沿后的数据访问时间                       | —                                                                                                                      | —   | 27 | ns  |

| <b>FRSTDATA 操作</b> |                                       |                                                                                                                        |     |    |     |

| $t_{24}$           | $\overline{CS}$ 下降沿到FRSTDATA三态禁用的延迟时间 | —                                                                                                                      | —   | 25 | ns  |

| $t_{25}$           | $\overline{CS}$ 下降沿到FRSTDATA高电平的延迟时间  | —                                                                                                                      | —   | 25 | ns  |

| $t_{26}$           | RD下降沿到FRSTDATA高电平的延迟时间                | —                                                                                                                      | —   | 25 | ns  |

| $t_{27}$           | RD下降沿到FRSTDATA低电平的延迟时间                | —                                                                                                                      | —   | 20 | ns  |

| $t_{29}$           | $\overline{CS}$ 上升沿到FRSTDATA三态使能的延迟时间 | —                                                                                                                      | —   | 24 | ns  |

CONVST 时序——转换之后读取

CONVST 时序——转换期间读取

并行模式时序——独立的 $\overline{CS}$ 和 $\overline{RD}$ 脉冲 $\overline{CS}$ 和 $\overline{RD}$ 相连的并行模式

串行读取操作

字节模式读取操作

时序图

## 功能框图

结构框图

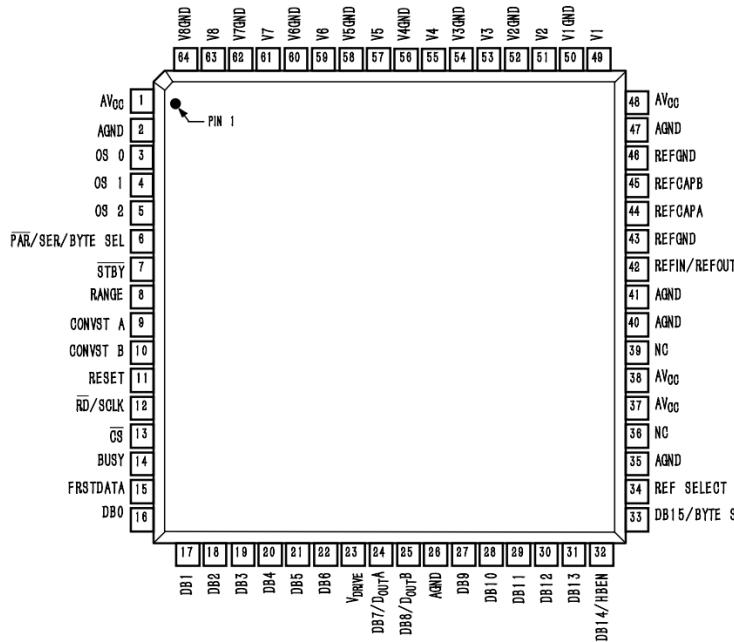

## 封装及引脚图

单位为毫米

| 尺寸符号 | 数值    |       |       | 尺寸符号 | 数值      |    |      |

|------|-------|-------|-------|------|---------|----|------|

|      | 最小    | 公称    | 最大    |      | 最小      | 公称 | 最大   |

| A    | —     | —     | 1.80  | e    | 0.50BSC |    |      |

| Al   | 0.00  | —     | 0.20  | b    | 0.12    | —  | 0.32 |

| D    | 11.70 | 12.00 | 12.30 | c    | 0.04    | —  | 0.25 |

| E    | 9.70  | 10.00 | 10.30 | L    | 0.40    | —  | 0.80 |

| E1   | 11.70 | —     | 12.30 |      |         |    |      |

外壳外形

| 管脚序号                  | 管脚名称             | 类型 | 管脚功能                                                                                                                                                                                                                                                                                                          |

|-----------------------|------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 37, 38, 48         | AV <sub>CC</sub> | P  | 模拟电源电压, 4.75V~5.25V。这是内部前端放大器和 ADC 内核的电源电压。应将这些电源引脚去耦至 AGND。                                                                                                                                                                                                                                                  |

| 2, 26, 35, 40, 41, 47 | AGND             | P  | 模拟地。芯片上所有模拟电路的接地基准点。所有模拟输入信号和外部基准信号都应参考这些引脚。所有 6 个 AGND 引脚都应连到系统的 AGND 平面。                                                                                                                                                                                                                                    |

| 5, 4, 3               | OS[2:0]          | DI | 过采样模式逻辑输入。这些输入用来选择过采样倍率。OS2 为 MSB 控制位, OS0 为 LSB 控制位。                                                                                                                                                                                                                                                         |

| 6                     | PAR/SER/BYTE SEL | DI | 并行/串行/字节接口选择输入。此引脚低电平则选择并行接口, 引脚高电平则选择串行接口。如果此引脚为逻辑高电平且 DB15/BYTESEL 为逻辑高电平, 则选择并行字节接口模式。<br>串行模式下 RD/SCLK 引脚用作串行时钟输入。DB7/DOUTA 引脚和 DB8/DOUTB 引脚用作串行数据输出。当选择串行接口时, 应将引脚 DB[15:9]和 DB[6:0]接地。<br>字节模式下, DB15 与 PAR/SER/BYTESEL 一同用来选择并行字节工作模式。 DB14 用作 HBEN 引脚。DB[7:0]通过 2 个 RD 操作传输 16 位转换结果, DB0 为数据传输的 LSB。 |

| 7                     | STBY             | DI | 待机模式输入。此引脚用来让器件进入两种省电模式之一: 待机模式或关断模式。进入何种省电模式, 取决于 RANGE 引脚的状态。待机模式下, 除片内基准电压、稳压器和稳压器缓冲外的所有其它电路均关断。关断模式下, 所有电路均关断。                                                                                                                                                                                            |

| 8                     | RANGE            | DI | 模拟输入范围选择。此引脚的极性决定模拟输入通道的输入范围。如果此引脚与逻辑高电平相连, 则所有通道的模拟输入范围为 $\pm 10V$ 。如果此引脚与逻辑低电平相连, 则所有通道的模拟输入范围为 $\pm 5V$ 。此引脚的逻辑状态改变会立即影响模拟输入范围。快速吞吐速率的应用, 转换期间建议不要更改此引脚的逻辑状态。                                                                                                                                              |

| 9                     | CONVSTA          | DI | 转换开始输入 A, 用来启动模拟输入通道转换。                                                                                                                                                                                                                                                                                       |

| 10                    | CONVSTB          | DI | 转换开始输入 B, 用来启动模拟输入通道转换。                                                                                                                                                                                                                                                                                       |

| 11                    | RESET            | DI | 复位输入。当设置为逻辑高电平时, RESET 上升沿复位器件。器件应                                                                                                                                                                                                                                                                            |

| 管脚序号  | 管脚名称                  | 类型 | 管脚功能                                                                                                                                                                                                                                                                                                                                           |

|-------|-----------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                       |    | 该在上电后收到一个 RESET 脉冲。RESET 高脉冲宽度典型值为 50ns。如果在转换期间施加 RESET 脉冲，转换将中断。如果再读取期间施加 RESET 脉冲，输出寄存器的内容将全部复位至 0。                                                                                                                                                                                                                                          |

| 12    | $\overline{RD}$ /SCLK | DI | 选择并行接口时为并行数据读取控制输入 $\overline{RD}$ ，选择串行接口时为串行时钟输入 SCLK。在并行模式下，如果 $\overline{CS}$ 和 $\overline{RD}$ 均处于逻辑低电平，则会启用输出总线。在串行模式下，此引脚用作数据传输的串行时钟输入。 $\overline{CS}$ 下降沿使数据输出线路 DOUTA 和 DOUTB 脱离三态，并逐个输出转换结果的 MSB。SCLK 上升沿将随后的所有数据位逐个送至串行数据输出 DOUTA 和 DOUTB。                                                                                         |

| 13    | $\overline{CS}$       | DI | 片选。低电平有效，使能数据帧传输。在并行模式下，如果 $\overline{CS}$ 和 $\overline{RD}$ 均处于逻辑低电平，则会使能输出总线 DB[15:0]，使转换结果输出在并行数据总线上。在串行模式下，利用 $\overline{CS}$ 使能串行数据帧传输，并逐个输出串行输出数据的最高有效位 MSB。                                                                                                                                                                             |

| 14    | BUSY                  | DO | 输出繁忙。CONVSTA 和 CONVSTB 均达到上升沿之后，此引脚变为逻辑高电平，表示转换过程已开始。BUSY 输出保持高电平，直到所有通道的转换过程完成为止。BUSY 下降沿表示转换数据正被锁存至输出数据寄存器，经过时间 $t_4$ 之后便可供读取。在 BUSY 为高电平时执行的数据读取操作应当在 BUSY 下降沿之前完成。当 BUSY 信号为高电平时，CONVSTA 或 CONVSTB 的上升沿不起作用                                                                                                                                |

| 15    | FRSTDATA              | DO | 数字输出。FRSTDATA 输出信号指示何时在并行、字节或串行接口上。回读第一通道 V1。当已输入为高电平时，FRSTDATA 输出引脚处于三态。 $\overline{CS}$ 下降沿使 FRSTDATA 脱离三态。在并行模式下，与 V1 结果相对应的 $\overline{RD}$ 下降沿随后将 FRSTDATA 引脚设为高电平，表示输出数据总线可以提供 V1 的结果。在 $\overline{RD}$ 的下一个下降沿之后，FRSTDATA 输出恢复逻辑低电平。在串行模式下，FRSTDATA 在 $\overline{CS}$ 下降沿变为高电平，因为此时将在 DOUTA 上输出 V1 的 MSB。在下降沿之后的第 16 个 SCLK 下降沿，它恢复低电平。 |

| 22~16 | DB[6:0]               | DO | 并行输出数据位 DB6 至 DB0。当 PAR 和 SER/BYTESEL=0 时，这些引脚充当三态并行数字输入 / 输出引脚。当 PAR/ $\overline{CS}$ 和 $\overline{RD}$ 均处于低电平时，这些引脚用来输出转换结果的 DB6~DB0。当 PAR 和 SER/BYTESEL=1 时，这些引脚应与 AGND 相连。当工作在并行字节接口模式时，D8[7:0] 通过 2 个 RD 操作输出 16 位转换结果。DB7(引脚 24) 为 MSB，DB0 为 LSB。                                                                                        |

| 23    | V <sub>DRIVE</sub>    | P  | 逻辑电源输入。此引脚的电源电压(2.3V 至 5.25V)决定逻辑接口的工作电压。此引脚的标称电源与主机接口(即 DSP 和 FPGA)电源相同。                                                                                                                                                                                                                                                                      |

| 24    | DB7/D <sub>OUTA</sub> | DO | 并行输出数据位 7(DB7)/串行接口数据输出引脚(DOUTA)。当 PAR 和 SER/BYTESEL=0 时，此引脚充当三态并行数字输入 / 输出引脚。当 $\overline{CS}$ 和 $\overline{RD}$ 均处于低电平时，此引脚用来输出转换结果的 DB7。当 PAR 和 SER/BYTESEL=1 时，此引脚用作 DOUTA。当工作在并行字节模式时，DB7 为该字节的 MSB。                                                                                                                                      |

| 25    | DB8/D <sub>OUTB</sub> | DO | 并行输出数据位 8(DB8)/串行接口数据输出引脚(DOUTB)。当 PAR 和 SER/BYTESEL=0 时，此引脚充当三态并行数字输入 / 输出引脚。当 $\overline{CS}$ 和 $\overline{RD}$ 均处在低电平时，此引脚用来输出转换结果的 DB8。当 PAR 和 SER/BYTESEL=1 时，此引脚用作 DOUTB，并输出串行转换数据。                                                                                                                                                      |

| 管脚序号   | 管脚名称               | 类型     | 管脚功能                                                                                                                                                                                                                                                                                |

|--------|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31~27  | DB[13:9]           | DO     | 并行输出数据位 DB13 至 DB9。当PAR和 SER/BYTESEL=0 时, 这些引脚充当三态并行数字输入 / 输出引脚。当CS和RD均处于低电平时, 这些引脚用来输出转换结果的 DB13 至 DB9。当PAR和 SER/BYTESEL=1 时, 这些引脚应与 AGND 相连。                                                                                                                                      |

| 32     | DB14/HBEN          | DO/DI  | 并行输出数据位 14(DB14)/高字节使能(HBEN)。当PAR和 SER/BYTESEL=0 时, 此引脚充当三态并行数字输出引脚。当CS和RD 均处于低电平时, 此引脚用来输出转换结果的 DB14。当PAR和 SER/BYTESEL=1 且 B15/BYTESEL=1 时, 器件工作在并行字节接口模式。在并行字节模式下, HBEN 引脚用来选择是首先输出转换结果的高字节(MSB)还是低字节(LSB)。<br>当 HBEN=1 时, 首先输出 MSB, 然后输出 LSB。<br>当 HBEN=0 时, 首先输出 LSB, 然后输出 MSB。 |

| 33     | DB15/BYTE SEL      | DO/DI  | 并行输出数据位 15(DB15)/并行字节模式选择(BYTESEL)。当PAR和 SER/BYTESEL=0 时, 此引脚充当三态并行数字输出引脚。当CS和RD 均处于低电平时, 此引脚用来输出转换结果的 DB15。当PAR和 SER/BYTESEL=1 时, BYTESEL 引脚用来在串行接口模式与并行字节 接口模式之间做出选择。当PAR和 SER/BYTESEL=1 且 DB15/BYTESEL=0 时, 器件工作在串行接口模式。当PAR和 SER/BYTESEL=1 且 DB15/BYTESEL=1 时, 器件工作在并行字节接口 模式。  |

| 34     | REF SELECT         | DI     | 内部 / 外部基准电压选择输入。逻辑输入。如果此引脚设为逻辑高电平, 则选择并使能内部基准电压模式。如果此引脚设为逻辑低电平, 则内部基准电压禁用, 必须将外部基准电压施加到 REFIN/REFOUT 引脚。                                                                                                                                                                            |

| 36, 39 | NC                 | —      | 悬空, 无需外围器件。                                                                                                                                                                                                                                                                         |

| 42     | REFIN/REFOUT       | REF    | 基准电压输入(REFIN)/基准电压输出(REFOUT)。如果 REF SELECT 引脚设置为逻辑高电平, 此引脚将提供 2.5V 片内基准电压供外部使用。可将 REF SELECT 引脚设置为逻辑低电平以禁用内部基准电压, 并将 2.5V 外部基准电压施加到此输入端。无论使用内部还是外部基准电压, 都需要对此引脚去耦。应在此引脚与 REFGND 引脚附近的地之 间连接一个 10 $\mu$ F 电容                                                                         |

| 43, 46 | REFGND             | REF    | 基准电压接地端。这些引脚应连接到 AGND。                                                                                                                                                                                                                                                              |

| 44, 45 | REFCAPA<br>REFCAPB | REF    | 基准电压缓冲输出强制/检测引脚。必须将这些引脚连在一起, 并通过低 ESR 10 $\mu$ F 陶瓷电容去耦至 AGND。这些引脚上的电压通常为 4.5V。                                                                                                                                                                                                     |

| 49     | V1                 | AI     | 模拟输入 1。                                                                                                                                                                                                                                                                             |

| 50     | V1GND              | AI GND | 模拟输入 1 地                                                                                                                                                                                                                                                                            |

| 51     | V2                 | AI     | 模拟输入 2                                                                                                                                                                                                                                                                              |

| 52     | V2GND              | AI GND | 模拟输入 2 地                                                                                                                                                                                                                                                                            |

| 53     | V3                 | AI     | 模拟输入 3                                                                                                                                                                                                                                                                              |

| 54     | V3GND              | AI GND | 模拟输入 3 地                                                                                                                                                                                                                                                                            |

| 55     | V4                 | AI     | 模拟输入 4                                                                                                                                                                                                                                                                              |

| 56     | V4GND              | AI GND | 模拟输入 4 地                                                                                                                                                                                                                                                                            |

| 57     | V5                 | AI     | 模拟输入 5                                                                                                                                                                                                                                                                              |

| 管脚序号 | 管脚名称  | 类型     | 管脚功能     |

|------|-------|--------|----------|

| 58   | V5GND | AI GND | 模拟输入 5 地 |

| 59   | V6    | AI     | 模拟输入 6   |

| 60   | V6GND | AI GND | 模拟输入 6 地 |

| 61   | V7    | AI     | 模拟输入 7   |

| 62   | V7GND | AI GND | 模拟输入 7 地 |

| 63   | V8    | AI     | 模拟输入 8   |

| 64   | V8GND | AI GND | 模拟输入 8 地 |

### 引出端排列及定义

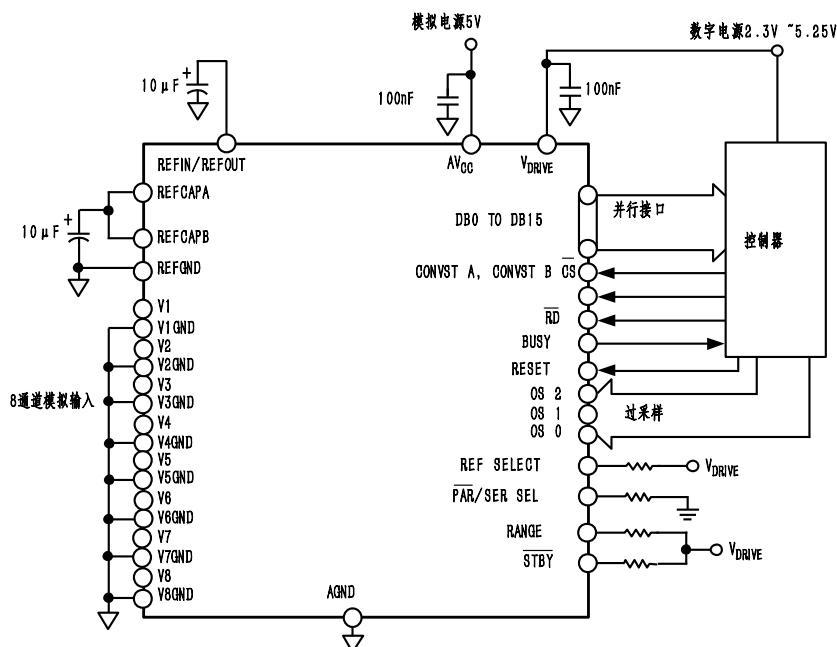

### 典型应用线路图

### 典型应用线路

### 注意事项

#### 1. 产品安装注意事项：

1. 注意电路的引出端排列，引出端方向错位容易烧坏电路；

2. 应关闭电源后再进行电路的插拔，否则易烧毁电路。

#### 2. 产品使用注意事项：

1. 从总线到每个节点的引出线长度应尽量短，以便使引出线中的反射信号对总线信号的影响最低；

2. 电源去耦。应在靠近器件电源引出端处用一只  $0.1\mu\text{F}$  和一只  $10\mu\text{F}$  的陶瓷电容器并联接地。

#### 3. 产品防护注意事项：

1. 该电路为静电敏感器件，虽然设计有 ESD 保护，但传递、使用、调试中如不注意 ESD 的保护，电路的输入、输出、使能端均会被 ESD 损伤，导致电路失效；

2. 应避免跌落，以免造成机械应力损伤等问题。

#### 4. 常见故障及处理办法:

##### 1.ESD 导致电路失效

该电路为静电敏感器件，虽然设计有 ESD 保护，但传递、使用、调试中如不注意 ESD 的保护，可能

会被 ESD 损伤，导致电路失效。

##### 2.工作电压超过最高工作电压失效

如果供电电压超过最高工作电压限制，会导致电路器件击穿失效，应保证供电电源不超过最大绝对

值。